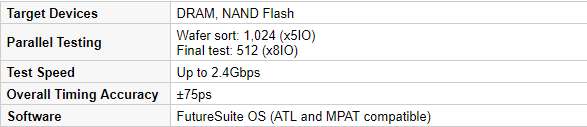

With a parallel test capacity of 2,048 devices for wafer test and 512 devices for final package test, the T5833 lowers costs by significantly reducing test time and boosting throughput. In addition to supporting known good die (KGD) testing at a maximum speed of 2.4 gigabits per second (Gbps), the T5833 also features a flexible site CPU architecture with multiple CPUs that enables optimized control of test processes.

The new system offers industry-leading capabilities in high-speed failure address storage and failure analysis, also known as memory redundancy. The speed of these two functions, both of which are indispensable for wafer sorting, reduces test time while enabling the recovery of more ICs for improved yield. In addition, both operations are scalable by making adjustments such as adding more CPUs for calculations.

Utilizing Advantest's AS modular memory test platform, the T5833 allows customers to choose the optimal system configuration for their needs, from engineering stations to large, volume-production systems. This extendibility allows the T5833 to handle future generations of devices and achieve higher throughput, which provides greater return on investment.

Thông số kỹ thuật